💻 计算机组成原理(PART C)

请注意,本文最近一次更新于:2022-07-25,文章内容可能已经不具有时效性,请谨慎参考

本文最后更新于:2022年7月25日星期一下午2点59分 +08:00

本系列的第三篇文章介绍8086的总线周期问题和半导体存储器问题

8086总线工作周期

时钟周期、总线周期、指令周期

执行指令的一系列操作都是在时钟脉冲信号CLK的控制下进行的,一个时钟脉冲时间称为

时钟周期,时钟周期由CPU的主频决定,是CPU定时的基准。8086CPU的主频为5MHZCPU与外部交换信息是通过总线进行的,CPU从存储器或外设I/O端口存储或读取一个字节或字所需要的时间称为

总线周期,一个基本的总线周期由4个时钟周期T1-T4组成 。一个总线周期完成一次数据传输,至少包括传送地址和传送数据两个过程。一个总线周期内的第一个时钟周期负责传送地址,剩下三个时间周期内负责传送数据。总线周期中允许插入等待周期Tw以保证数据读写执行完全。当总线上无数据传输操作时,总线处于空闲状态,此时执行空闲周期Ti。对8086来说,总线周期有六种:存储器读周期、存储器写周期、I/O读周期、I/O写周期、中断周期、取指令周期 一条指令的执行包括取指令、分析指令和执行指令。一条指令从最开始取指令到最后执行完毕所需要的时间称为一个

指令周期,一个指令由一个或若干个总线周期组成 ,不同的指令一般有不同长度的指令周期8086处理器的最小与最大工作模式

最小模式用于由8086单一微处理器构成的小系统,最小模式下,由8086CPU直接产生小系统所需要的全部控制信号。该系统的特点是:总线控制逻辑直接由8086CPU产生和控制 ,当8086CPU以外的模块想占用总线周期时,可以向CPU提出请求,在CPU允许并响应的情况下将获得总线控制权,使用完毕后归还给CPU最大模式用于实现多处理机系统,其中8086CPU被称为主处理器,其他处理器被称为协处理器。在这种模式下,8086不直接提供用于存储器或I/O读写的命令的控制信号,而是将当前执行的操作类型经3个状态为输出,经译码器译码后,经由总线控制器8288产生相应控制信号。该系统的特点是:总线控制逻辑由总线控制器8288产生和控制 8086微处理器结构

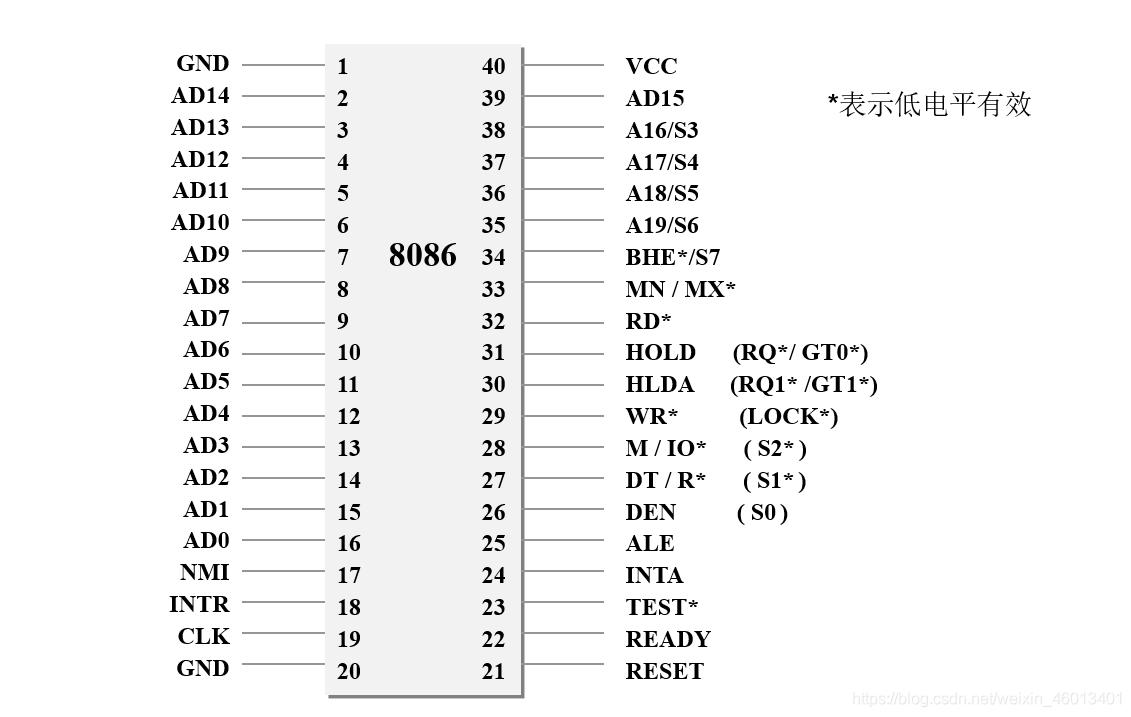

- 8086采用了

引脚复用技术 - 结构图:括号内为最大模式下的引脚名称

- 8086引脚功能

两种模式下功能相同的引脚

- AD0 —— AD15:地址/数据复用接口,双向性,三态性(低电平、高电平、高阻态);在T1时钟周期用作地址线(输出地址的低16位),在T2-T4时钟周期用作数据线使用

- A19/S6 —— A16/S3:地址/状态复用接口,输出,三态;在T1期间用作地址线,对于存储器访问来说,输出地址的最高四位;对于I/O访问来说,由于只使用16位地址,所以T1期间内这四根线将处于低电平无效。在T2-T4期间内,这四根线用作状态线使用。S6指示当前8086是否正在使用总线、S5指示中断允许标志位IF的状态、S4&S3指示正在使用的段寄存器

- $\overline{BHE}$/S7:控制/状态复用接口,输出,三态;T1期间作为高8位数据传送允许信号,在T2-T4期间作为输出状态信号。

- $\overline{RD}$:读控制、输出、三态。有效时表示CPU正在从存储器或I/O端口读取数据

- READY:准备就绪、输入。有效时表明不需要插入等待时钟Tw

- INTR:可屏蔽中断请求,输入

- $\overline{TEST}$:测试。输入,无效时指示CPU继续插入空闲等待周期Ti

- NMI:非屏蔽中断请求,输入

- RESET:复位,输入

- CLK:时钟,输入

- VCC:+5V电源输入引脚

- GND:接地引脚

- MX/$\overline{MX}$:组态选择,输入;该引脚接+5V时工作在最小模式,接地时工作在最大模式

两种模式下功能不同的引脚

最小模式下

- $\overline{WR}$:写控制,输出,三态;有效时表示CPU正在向存储器或I/O端口写入数据

- M/$\overline{IO}$:存储器/IO操作,输入,三态;高电平时表示存储器操作,低电平时表示I/O操作

- $\overline{INTA}$:中断响应,输出;CPU响应

可屏蔽请求INTR后进入中断响应周期。8086中断响应周期为两个,因此在中断响应周期内会发出两个INTA - ALE:地址锁存允许,输出,三态;有效时,表示复用地址线增在传送地址信息,下降沿到来时用于进行地址锁存

- DT/$\overline{R}$:数据收/发控制,输出,三态;高电平时,表示数据从CPU流出,CPU向外输出数据;低电平时表示数据流入CPU,CPU接收数据

- $\overline{DEN}$:数据允许,输出,三态;有效时表示允许数据传送

- HOLD:总线持有请求(总线请求),输入;有效时,表示总线控制设备(总线请求设备)向CPU申请占有总线

- HLDA:总线持有响应,输出;有效时,表示CPU响应HOLD请求并已释放总线,此时CPU的地址、数据、控制总线将全面呈现高阻态,便于提出请求的总线控制设备顺利接管总线

最大模式下

- $\overline{S2-S0}$:状态信号,输出,三态;8086通过这三维的编码让总线控制器8288了解8086当前工作状态

- $\overline{LOCK}$:总线锁定,输出,三态;有效时,将封锁其他总线控制设备,不允许他们此时提出HOLD请求,直到CPU将当前指令执行完毕为止

- QS1,QS0:指令队列状态,输出;通过这两位编码让外部电路了解指令队列当前操作状态

- $\overline{RQ0/GT0}$、$\overline{RQ1/GT1}$:请求/同意,双向,三态;与最小工作模式下的HOLD与HLDA功能类似

- 8086采用了

半导体存储器

概述

计算机采用

连续存储原理以保证计算机自动、连续地工作,实现这一原理需要存储器存储器是计算机系统中的记忆设备,用来存放程序和数据

现代微机系统中存储器地典型结构是一个

快慢搭配、具有层次结构的存储系统,它呈现金字塔结构,从塔尖到基座运行读写减慢、容量增大,以此为CPU寄存器、CPU内部高速缓存、主板高速缓存、主存储器、辅助存储器和大容量辅助存储器存储器分类

- 构成存储器的存储介质主要采用

半导体器件和磁性材料,一个存储元存储一位二进制代码,即一个比特,存储器中最小的存储单位称为`存储位`或`存储元`,由若干个存储元构成一个`存储单元`,多个存储单元构成一个`存储器` 。一般地,一个存储单元能够存储一个8位二进制信息,即一个字节 - 分类

- 存储介质:

半导体存储器、磁表面存储器、光盘存储器半导体存储器的存储元件由半导体器件组成,优点是体积小、功耗低、存取时间短;缺点是断电时存储信息就会丢失,是一种

易失性存储器,按照制作工艺不同可以进一步分为双极型、MOS型存储器,前者存取速度快,后者集成度高、制造简单、成本低廉、功耗小。当前的主流半导体存储为MOS型磁表面存储器是金属或塑料基体的表面上涂抹磁性材料作为记录介质,工作时由磁头在磁层上进行读写操作。采用的材料具有

磁滞回线特性,因此具有非易失性光盘存储器是应用激光在记录介质(磁光材料)上进行读写操作的存储器,同样具有

非易失性,具有记录密度高、耐用性好、可靠性高和可互换性强的特点 - 存取方式:

随机存储器、只读存储器、顺序存取存储器、直接存取存储器随机存储器RAM是一种

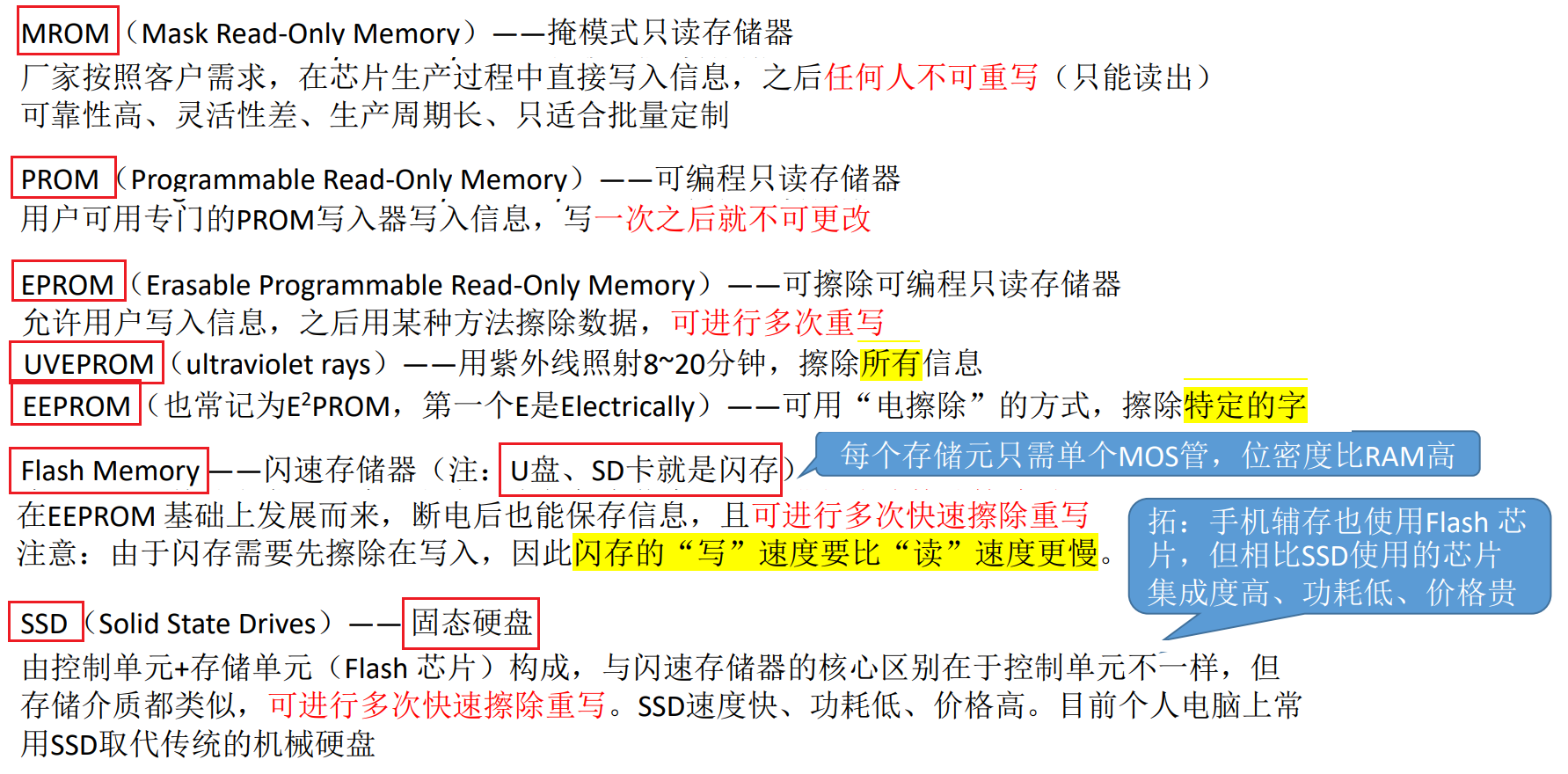

可读写存储器,存储器中的任何一个存储单元的内容都可以随机存取,且存取时间与存储单元的物理位置无关,计算机系统中的主存都采用这种随机存储器。暗潮存储信息原理的不同,进一步分为静态随机存储器SRAM、动态随机存储器DRAM。SRAM只要不掉电,存储信息就不会丢失,且速度比DRAM快,但集成度低于DRAM,功耗高于DRAM,一般用作高速缓冲存储器;DRAM需要配备专门的刷新电路,否则容易丢失信息,优点是集成度高,价格低廉,一般用于大存储容量的系统中只读存储器ROM只能对存储的内容进行读出而不能对其重新写入,通常用于存放固定不变的程序、常数以及汉字,以及用于操作系统固化等。进一步可分为

掩膜式MROM、可编程PROM、可擦除EPROM、电可擦除EEPROM、闪存Flash Memory

串行访问存储器是按物理位置的先后顺序寻找地址的存储器,进一步分为顺序存取存储器和直接存取存储器

- 作用分类:

主存储器、辅助存储器、缓冲存储器主存储器的主要特点是他可以和CPU直接交换信息,主要由半导体存储器构成,也称为

内存储器。主存速度快,但容量小价格高辅助存储器是主存储器的

后援存储器,用来存放当前暂时不用的程序和数据,它不能与CPU直接交换信息。辅存速度慢但容量大,价格低缓冲存储器用在两个速度不同的部件之间,比如CPU与主存之间就设置有一个快速缓冲存储器,用来提高CPU访问存储器的速度

- 存储介质:

- 构成存储器的存储介质主要采用

存储器性能指标

- 存储器容量

存储器的容量是指存储器所能容纳的最大字节数,存储器的容量越大,计算的运行的速度也就越快

存储芯片是由许多的存储元组成的,在物理结构上,这些存储元(基本存储单元)按照一定规律排布成适当的阵列,这

种由存储元组成的阵列称为存储矩阵对存储芯片进行操作时,一次 只能选中存储矩阵中固定数目的存储元,将这些存储元合在一起称为一个

芯片字

(存储单元),对存储芯片的操作是以芯片字为单位进行的。一个芯片字包含了若干个(数目是固定的)存储元,也称为包含若干位,比如现在人们耳熟能详的32位、64位,表示一次可以同时对4个、8个单元进行访问在对存储器进行读写操作时,仍然是以存储单元位基本单位,即以字节为基本单位进行的

芯片的容量=存储单元数目×位数

- 存取周期

存储器的存储周期是指从接收到地址,到实现一次完整的读出或写入数据需要的时间,是存储器进行连续读或写操作所允许的最短时间间隔

计算机的运行速度与存储器的存取周期有着直接的关系

一个存储系统的存取周期不仅与存储器芯片的存取周期有关,而且还与存取路径中的缓冲器以及地址/数据线的延时有关

- 功耗

- 可靠性

- 集成度

- 存储器容量

This is an identification card as an honored membership of FeynmanDirac

Happy to see you follow FeynmanDirac, enjoy science together

验证码启动中...

验证码启动中...

备用人机验证